## DESIGNE 2019 MAGAZINE

## Everything Starts WITH Design

## Our library is the bookmobile for the 21st century.

Registered members of **my I-Connect007** have access to our ever-growing library of eBooks, which now includes a wide range of topics from DFM to thermal management.

Instead of waiting for the bookmobile, though, our users download new titles with the click of a mouse. It's pretty awesome!

### View our eBook library

## Your how-to guide for making Rev 1 work.

In this book, readers will learn how to design complex boards correctly the first time, on time. A must-read for anyone designing high-speed, sophisticated printed circuit boards. THE PRINTED CIRCUIT DESIGNER'S GUIDE TO....

## **Executing Complex PCBs**

Scott Miller Freedom CAD Services

1.007 Books

DOWNLOAD NOW

I-007ebooks.com/ecd

#### JUNE 2019 • FEATURED CONTENT

## DESIGNOOT MAGAZINE

16

## Everything Starts With Design

Designers were once seen as little more than electronic techs. Now, many designers are starting to realize the power they wield over the whole electronics process. As you'll learn in this issue, there are plenty of little things that a designer can do to help make the board easier to fabricate and assemble, and even influence the profitability of the final product.

**Design Is a Pivotal Piece of the Puzzle** Interview with Julie Ellis

- 24 Albert Gaines: Design All Comes Down to Documentation Interview with Albert Gaines

- 28 Design for the Unknown by Kelly Dack, CID+

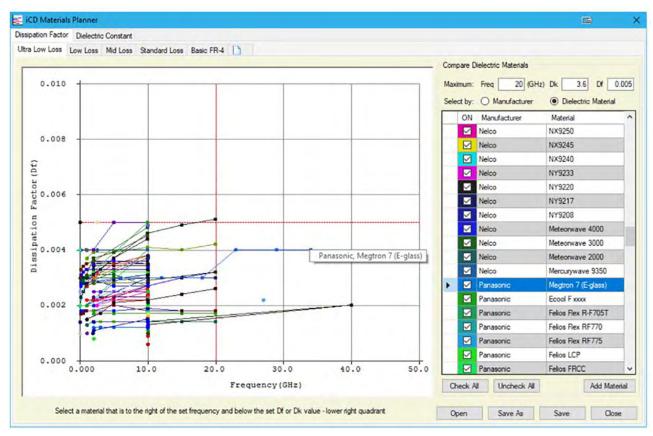

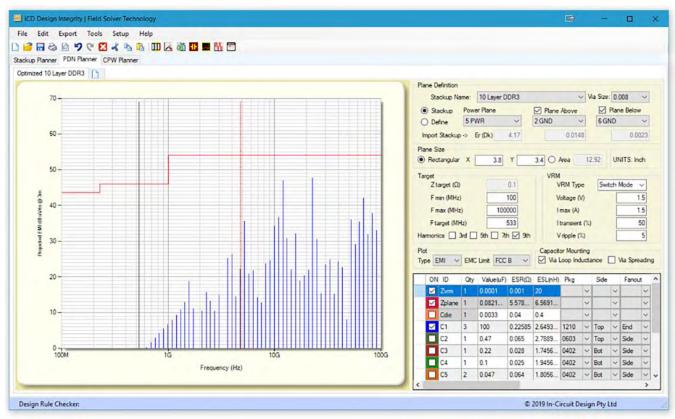

38 Technically Appropriate Material Choices Are Key to Success Interview with Mike Creeden

### FEATURE COLUMNS:

- 10 Fabrication Starts With Solid Design Practices by Mark Thompson

- 32 Clear Communication Takes the Cake by Tim Haag

## **30+ YEARS EXPERIENCE. MORE THAN 30 PATENTS. JUST ONE GOAL.**

Flexible Printed Circuits

Flat Flexible Cable

Wire Harnesses

Providing a quality, cost-effective solution on time has been our goal since day one. We achieve this through unparalleled customer service and by designing, sourcing and finishing interconnection systems for our customers worldwide.

Miraco, Inc. Manchester, NH miracoinc.com 603-665-9449

MIRACO

#### JUNE 2019 • ADDITIONAL CONTENT

##

#### SHORTS:

- **Researchers Identify New 2D Insulators** 14 With Ferromagnetics Properties

- KLM Partners With TU Delft to 97 Make Aviation More Sustainable

- New Interaction Between Thin Film 36 **Magnets Discovered**

- Accurate Probing of Magnetism With Light 53

- 63 Flexible Generators Turn Movement Into Energy

WANTE

- 70 **AI-Driven Imaging System Protects Authenticity**

- New Approach Captures Detailed Mid-infrared 75 **Images for Medical Diagnostics**

- 83 **Radar Sensor Module to Bring Added** Safety to Autonomous Driving

#### **DEPARTMENTS:**

- 87 **Career Opportunities**

- 96 **Events Calendar**

**ARTICLE:**

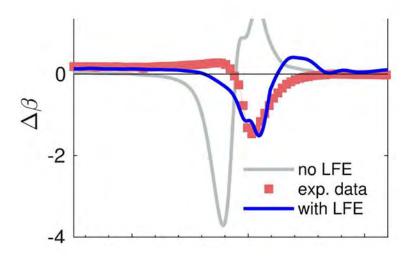

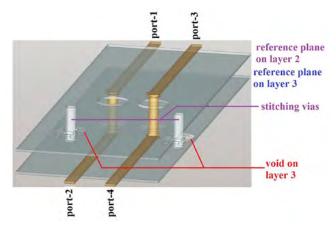

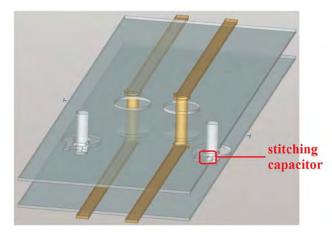

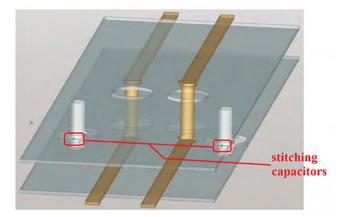

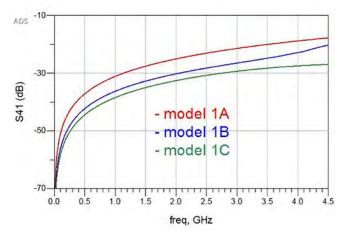

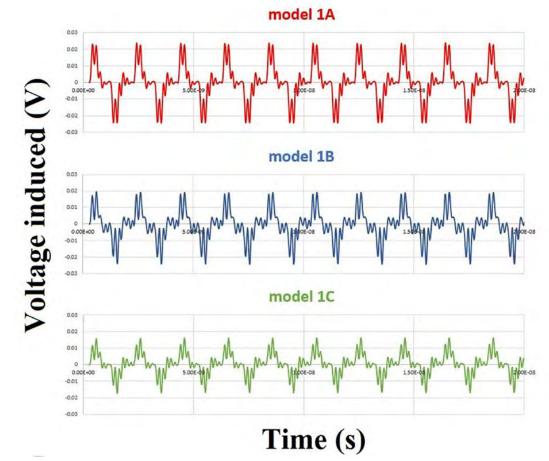

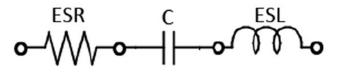

**Stitching Capacitor: Crosstalk Mitigation** 78 for Return Path Discontinuity by Chang Fei Yee

#### COLUMNS:

- **Everything Starts With the Designer** 8 by Andy Shaughnessy

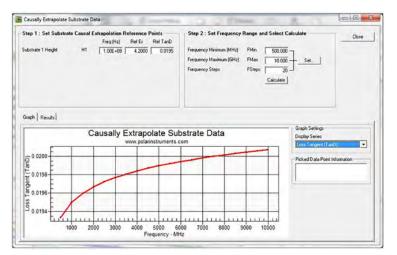

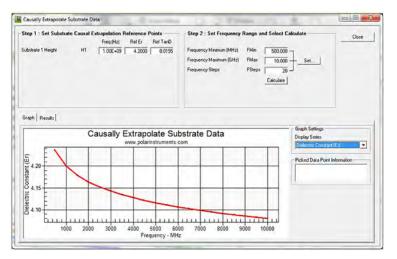

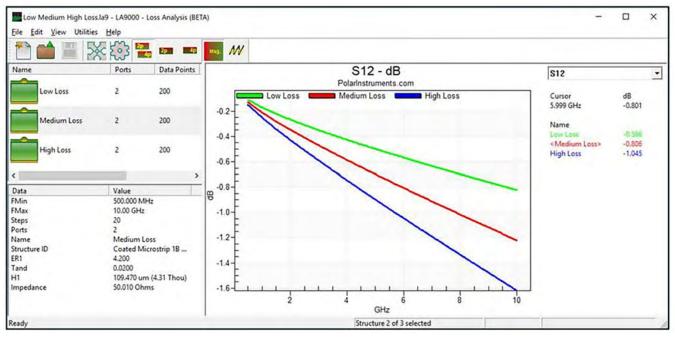

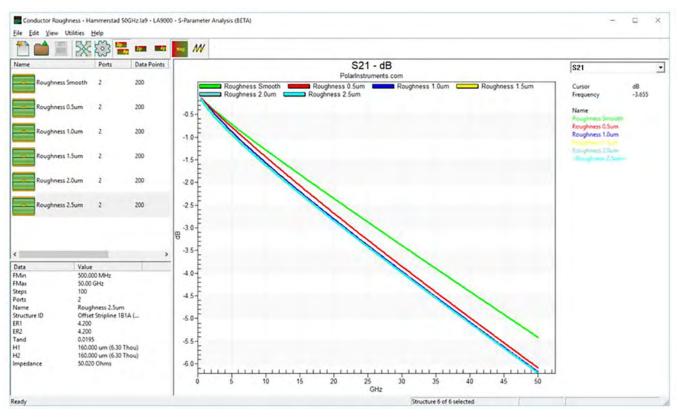

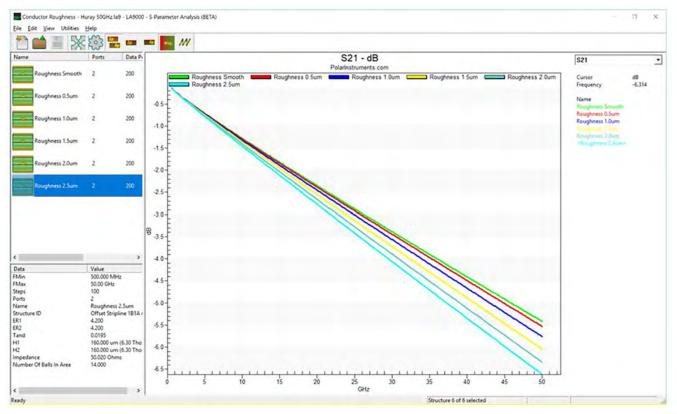

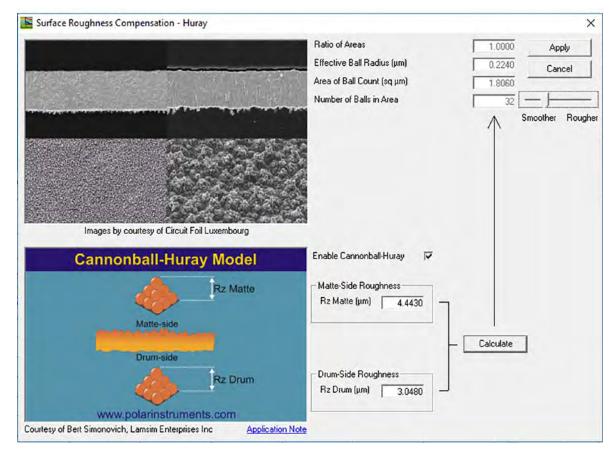

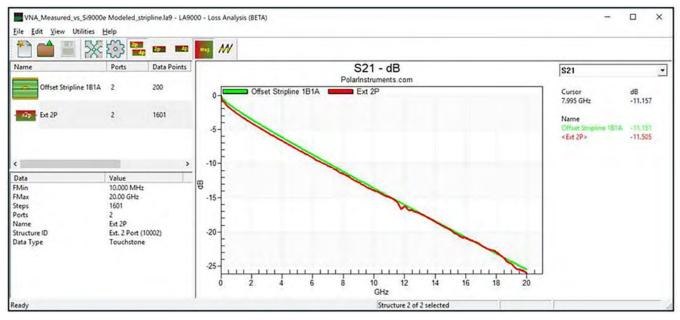

- Modelled, Measured, Mindful: 44 **Closing the SI Loop** by Martyn Gaudion

- 50 Chapter Check-ins: Orange County, San Diego, and Phoenix by Stephen Chavez

- 54 The Future of PCB Manufacturing Doesn't Belong to Robots, but to the Users by Bob Tise

- **Resins Fit for a Purpose: Failure Mitigation** 60 and Environmental Concerns by Alistair Little

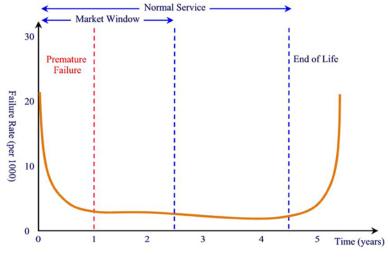

- 64 The Key to Product Reliability by Barry Olney

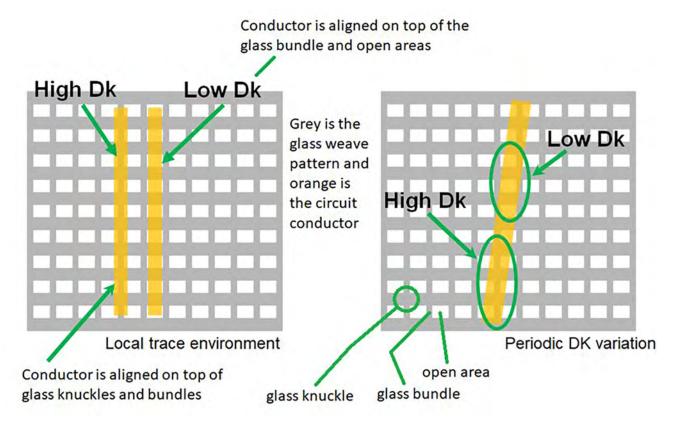

- **Practical Evaluations of** 79 **Glass Weave Effect** by John Coonrod

- 42

- 76 MilAero007

- Top 10 PCBDesign007 84

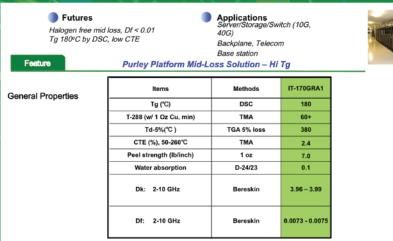

## IT-170GRA1

### IT-170GRA1 Value Proposition

- Halogen Free

- Best in class performance in its space

- •Best in class CAF performance

- Very attractive price to performance ratio

- Pass MRT-6 requirements

- -CAF > 1000 hours

- -0.65mm pitch equivalent, no thermal issue

- •Available with RTF and 2µ copper which provides additional

- performance on a very solid platform

- •Df = 0.0075 @10GHz

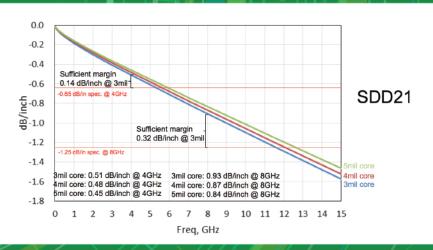

### Intel Purley Mid-Loss Solution – IT-170GRA1

IT-170GRA1 Insertion Loss

ITE

# Everything Starts With the Designer

The Shaughnessy Report by Andy Shaughnessy, I-CONNECTO07

Once upon a time in the not-too-distant past, PCB designers were the Rodney Dangerfields of the electronics industry. They didn't get no respect, and in some cases, not much of a salary either. But times have changed. Now, many

designers are starting to realize the power they wield over the whole electronics process.

The folks downstream in fabrication and assembly understood this sentiment long ago, usually expressing it as, "It's the designer's

fault." But recently, a variety of manufacturers have told me, "Everything starts with design."

That's certainly a more positive spin! Everything does start with design—the positive outcomes as well as the negative. The designer can control much of the development of the PCB, and often the final product, with a little planning during the earliest part of the design cycle. It's a designer's responsibility to do everything possible to avoid getting that call from the CAM department at 5:30 p.m. on a Friday.

We surveyed our designer readers in preparation for this issue. Here's one of the more pertinent questions: What steps do you take to make the job easier for your fabrication and assembly providers? Here are a few of the replies:

- Communicate directly with them, especially if you want to try something new

- Follow proven design methodologies and rules

- Get feedback on previous builds to improve upcoming projects

- Try to insist that the fab house runs Valor DFM

- Minimize layer count

- Use the largest trace widths, via sizes, and clearances we can

- Don't use more demanding fab technology than absolutely necessary

- Plan your stackup with your fabricator

- Reduce the drill count

- Follow IPC standards

A lot of the replies were variations on these themes: Communicate. Don't throw your downstream partners any technological curve balls. Go big if at all possible, except for layer count. Follow IPC guidelines.

All of this might make us think that the days of throwing the design "over the wall" are just about over. But there are still flies in the proverbial oatmeal. We know that communication is still a big problem; many designers never speak to their fabricator until they get that Friday evening phone call. But many designers say that they have no earthly idea where their boards are going to be manufactured. They just design each board so that it can, hopefully, be fabricated anywhere.

As you'll see in this issue, there are plenty of little things that a designer can do to help make the board easier to fabricate and assemble, and even influence the profitability of the final product.

In our first feature, Prototron's Mark Thompson, CID +, explains why great fabrication jobs always start with solid design practices, and he lays out some of the things designers should—and should not—do to help make the design more manufacturable. Then, in an interview with our editorial team, Julie Ellis of TTM discusses some of the tips and tricks designers should adopt, especially if their boards are going to be built in Asia. As Julie says, you need to know your fabricator's capabilities or you could be up a creek without a paddle.

We also have an interview with Al Gaines, founder of HiGain Design Services. He takes "everything starts with design" one step fur-

ther: Everything starts with documentation, which Al describes as the most critical product that each designer can create. Next, Kelly Dack, an IPC CID designer instructor with EP-TAC, introduces us to his idea for the ultimate in DFX: Design for the Unknown, or DFU. Kelly also offers some advice for dealing with one of the newest cogs in the machine: the industrial designer.

Columnist Tim Haag explores the relationship between good PCB design processes and the recipe for a birthday cake; changing one ingredient can change the entire outcome! And we have a short interview that Nolan Johnson conducted with Mike Creeden of San Diego PCB Design. Mike discusses the need to select the appropriate type of laminate as early in the design process as possible.

Yes, everything starts with design. You may have already known that, but now your downstream partners do as well. We'll do everything we can to help you along the way.

See you next month! DESIGN007

Andy Shaughnessy is managing editor of *Design007 Magazine*. He has been covering PCB design for 19 years. He can be reached by clicking here.

## Fabrication Starts With Solid Design Practices

The Bare (Board) Truth Feature Column by Mark Thompson, CID+, PROTOTRON CIRCUITS

"All right! Don't rush me. I'm a-thinking... and my head hurts." —Yosemite Sam

It's a fact: Great board design is the key to a great PCB. I'm even more certain of this after spending two days in a wonderful class presented by Rick Hartley titled "Control of Noise, EMI, and Signal Integrity in High-speed Circuits and PCBs."

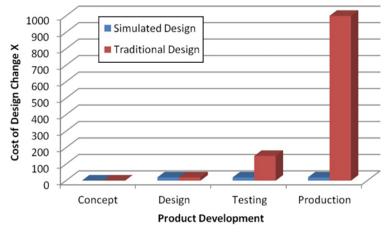

First, I would like to thank Rick for teaching his course. I thought I had a pretty decent grasp of controlled impedance and signal integrity, but the gaps in my knowledge base can fill the Grand Canyon. This class helped me see how important the design truly is not only for functionality but also for minimizing revisions and passing EMI testing the first time. I deal with incoming designs for a living, but I had no idea how many things you should consider when doing a board layout, from part placement and organization to via location. I guess I am just accustomed to simply using my field solver and answering fabricationrelated questions to make a PCB producible. I thought I knew it all, from effective Dk and Er to layer "nesting" based on the layer interfaces and prepreg selection for various controlled impedance structures. I assumed I knew what I needed to know from how the color and dielectric of a mask can affect controlled impedances to the use of ultra-thin dielectrics to increase inductance to pass EMI. Well, I was wrong!

How far we have come from the days of slower-speed designs; their edge rates didn't matter very much because they were are basically lumped elements. Those old designs are nothing like today's high-speed designs and all the bugaboos associated with distributed length line designs. Understanding the impact of nearby traces on controlled impedance lines and how magnetic fields work can make the

Powerful Schematic Capture and PCB Design Software

## Are you looking for cost effective **PCB Design Software?**

## Look no further, **Pulsonix** is the answer

- Very easy to learn and use

- Co-design in integrated PCB/3D design environment

- Import design data from your existing CAD tool

- High Speed design with Constraint Manager

- Free access to over 13 million library parts

- STEP integration with Mechanical CAD

- Reverse Engineer feature to PCB from Gerber files

## Download a FREE trial from **pulsonix.com**

Contact us today and see how Pulsonix can work for you:

Email sales@pulsonix.com

## www.pulsonix.com

difference between a successful design and a quagmire of self-created issues, such as common-mode emissions that can make or break passing EMI testing.

I even learned a few things about via filling with silver-epoxy or copper-epoxy for thermal applications. Remember, if you are using a via fill for conductivity, you are missing the point; the electromagnetic fields are generated around the barrel of the holes, not the material filling the hole. In some cases during Rick's presentation, I wanted to slap myself in the forehead and say, "I should have had a V-8!"

## Remember, if you are using a via fill for conductivity, you are missing the point.

Rick showed one slide with four examples to be rated from least to most of radiated EMI. Fortunately, they are the same as a firing order in most four-cylinder combustion engines (1, 3, 4, 2) and pretty much everyone understood not to rout a trace over a split or a slot.

On many occasions during Rick's presentation, I began to make sense of some of the crazy things we have been asked as a fabricator over the years. Eight years ago, one customer asked us to mill a channel in a thick PCB using an end mill to make the corners as square as possible (not routed with a radii) and plate the trough and cap the whole structure with what appeared to be a wide plated "trace" running the entire length and width of the channel. At either end was a small hole where I was told they would inject a liquid. Then, I saw Rick's slide saying, "Apply a wave whose half wavelength is equal to distance X. We have a perfect balance and a true waveguide."

We were basically creating an acoustic waveguide through the Z-axis of a PCB. A 1995 article by L. Dwynn Lafleur and F. Douglas Shields of the Acoustical Society of America noted, "It is shown that certain combinations of material properties can produce a mode, which in zero frequency limit, has plane-wave motion in the liquid." This is presumably why the customer was injecting liquid into the waveguide. Great stuff!

I did know a few things that Rick covered in his class, like routing longer differential pairs and clocks inside the PCB and keeping the shorter traces to the outer layers. But I only thought I knew why; when solving for impedances internally, the differential pairs and single-ended structures are more forgiving. The electromagnetic wave field is not completely contained in the substrate as with a stripline used internally where the EM field is contained within the substrate. This is at least partially due to the Dk of air over the trace on an outer layer.

#### **Great Fabrication Starts With Great Design**

Again, I remember when I was asked to review a design for a customer from the standpoint of manufacturability. It was an 18-layer board where all layers had impedances. The layers had reference planes like a checkerboard above and below signals alternating back and forth on every layer.

From a pure design perspective, it was a work of art. But could it be produced? It turned out that all the traces were laid out with the same trace width and different spaces (for multiple differential pair scenarios of 90, 100, and 120 ohms) and ground separations on every layer. In conjunction with that, all of the copper pour used the same trace width they had used for the signals—both single-ended and differential pairs.

There were five different scenarios with the same trace width, making it virtually impossible to tweak any of the signal traces, and all of this had to be done through changes to dielectrics and material type. I spent the better part of a day looking at what could be done and came up with a specific dielectric and material combination to make it all work without having to change the trace widths at CAM. With five different scenarios, that would have been a nightmare.

Along with the stackup and material type, I said that the design would benefit from chang-

ing the trace width size from five different scenarios to five different trace widths by onetenth or one-hundredth of a mil. This was with the knowledge that the slight variations could not be resolved in fabrication, but this would allow a CAM operator to resize the unique trace widths without affecting the other scenarios. Once everything was said and done, I presented the material type and dielectrics to the customer, who promptly said, "No, that material won't work for us."

The best-laid plans do not always work in fabrication. That part was eventually redesigned to reduce the layer count, opening up the possibilities for dielectric changes, highspeed materials, and reduced impedance scenarios. It also had five trace widths from the same size to one-tenth or one-hundredth of a mil for us to pick them out for resizing to meet the desired impedances.

After reading all of this, you're probably thinking, "What is your point?"

I cannot overemphasize the need to check with your fabricator before starting layout, from the proper Er of the material you are using to modeling the impedances with a true field solver and questions about the mask dielectrics and Er data associated with the mask.

Just 10 years ago with 0.008"/0.008" spaces and traces, it was no big deal to have a mil or two of mask over the trace. But with today's geometries of 0.003"/0.003", that extra mil of mask will definitely affect the impedances. Before you lay out a part that may have to change (which nobody likes), consult your chosen fabricator.

#### "Helping" Your Customer

This is also known as "How did we get into this mess?" Let me give you an example.

Let's say the customer provides internal plane relief pads that are undersized based on your capabilities. But you say, "It is only a fourlayer. Starting with 0.006" clearances from the edge of the non-drill-compensated plated hole will leave us with approximately 0.004"." But you are able to pull it off for that job.

The customer thinks all the designs can use that same relief size, so they send a 14-layer with the same relief sizes. This time, the person previewing the job says this won't fly and asks the customer to increase the relief sizes. Then, the customer is NOT happy, because they do not have the time to lay out the entire job again, saying, "Well, you did it on the four-layer last week." Now, you have an upset customer solely because you were trying to do them a favor on the four-layer, which you were not when you suggested that they could live with the undersized reliefs.

The customer has a 14-layer and has used the same insufficient relief sizes. This is why we have capability minimums that should not be busted, even on the four-layer, unless the customer is made aware that they are risking internal misregistration issues and that you can do this one time. Do not make it the norm.

These types of conversations should take place between a pre-engineering person and the designer, not a manufacturing person or a salesperson. You are doing the customer a disservice by "pulling something off" when the risks of doing so should be clearly described to the customer. Don't be that fabricator!

Another issue we should discuss is drill files. It seems that fairly often, the NC drill file comes in with a totally different numerical format than the artwork. Sometimes, blind vias, buried vias, and through-holes all arrive with different numerical formats, leaving the preview person to figure out what the format should be.

### It seems that fairly often, the NC drill file comes in with a totally different numerical format than the artwork.

It's true that looking at the NC drill file coordinates can help determine whether the format should be leading zero suppression, trailing zero suppression, or no zero suppression. Some come in as a mix of metric for tools and imperial for dimensions and vice versa, and the format is frequently different from that of the image data. Presumably, if you have a specific format for the image data, the NC drill file should have the same numeric tolerance, so mixing numeric data formats should be avoided. The most typical NC drill format is set to "inch" for both the tool size and the dimensions. The most used formats are 2:4 (for positional accuracy) and trailing zero suppression.

Now that I have gotten off my soapbox, let me end by saying that a good CAM operator can always figure out the proper numerical format to match the NC drill drawing. But do yourself a favor by at least making them consistent. Don't make the non-plated tool file one format and the plated holes another. Likewise, do not make the blind vias, buried vias, and through-holes all different numerical formats.

As Rick often says, "Don't take things for granted and don't believe everything you read until you have proved them for yourself empirically or by making mistakes."

Thanks again, and as always, feel free to contact me any time. **DESIGN007**

Mark Thompson is in engineering support at Prototron Circuits. To read past columns or contact Thompson, click here. Thompson is also the author of *The Printed Circuit Designer's Guide to... Producing the*

*Perfect Data Package.* Visit www.I-007eBooks.com to download this book and other free, educational titles.

## **Researchers Identify New 2D Insulators With** Ferromagnetic Properties

Collaborating scientists at the U.S. Department of Energy's Ames Laboratory, Brookhaven National Laboratory, and Princeton University have discovered a new layered ferromagnetic semiconductor, a rare type of material that holds great promise for next-generation electronic technologies. The researchers discovered ferromagnetism in a vanadium-iodine semiconductor, a material which has long been known but ignored.

"Being able to exfoliate these materials down into 2D layers gives us new opportunities to find unusual properties that are potentially useful to electronic technology advances," said Tai Kong, a postdoctoral researcher in the lab of Robert J. Cava, the Russell Wellman Moore Professor of Chemistry at Princeton University. "It's sort of like getting a new shape of Lego bricks. The more unique pieces you have, the cooler the stuff you can build."

The advantage of ferromagnetism in a semiconductor is that electronic properties become spin-dependent. Electrons align their spins along internal magnetization.

"This creates an additional control knob to manipulate currents flowing through a semiconductor by manipulating magnetization, either by changing the magnetic field

> or by other more complex means, while the amount of current that can be carried may be controlled by doping (adding small amount of other materials)," said Ames Laboratory Scientist Ruslan Prozorov. "These additional ways to control behavior and the potential to discover novel effects are the reason for such high interest in finding insulators and semiconductors that are also ferromagnets."

(Source: Princeton University)

"Mark does an outstanding job detailing what needs to be included in the handoff from designer to fabricator. This book should be required reading for every designer."

Producing the Perfect Data Package

**Mark Thompson Prototron Circuits**

Douglas Brooks, Ph.D. THE PRINTED CIRCUIT DESIGNER'S GUIDE TO... **BS/MS EE**

Most of the design data packages that a fabricator receives contain inaccurate or incomplete data.

Don't be a data violator!

I-007eBooks.com/data

## Design Is a Pivotal Piece of the Puzzle

#### Feature by the I-Connect007 Editorial Team

As a field applications engineer at TTM Technologies, which has fabrication and manufacturing locations around the world, Julie Ellis sees a wide variety of customer design requirements. In this interview with the I-Connect007 Editorial Team, Julie explains how PCB designers can influence the development of the PCB. She shares a variety of tips and tricks that designers can implement early in the design process to help optimize fabrication and assembly later on and keep small issues from becoming big problems downstream.

**Andy Shaughnessy:** Julie, with your job you have a pretty circumspect view of design and manufacturing. Can you start by giving us an idea about your job and some of the designs that you see crossing your desk?

**Julie Ellis:** My main task is to support customers' designs for manufacturability by understanding their requirements and providing

stack-ups and design guidelines for rigid circuit boards that are within TTM fabrication capabilities and process tolerances. I also help customers understand how fabrication processes affect capabilities, so they accept design modifications that assist in manufacturing.

The work I see coming across my desk includes components for EV charging and power conversion, Lidar, radar, back-up and industrial scanning cameras, ultrasound, defibrillators, and glucose monitoring. They require stack-ups ranging from four-layer heavy copper boards to 32 layers with three lamination cycles and mechanical blind holes and advanced HDI, which I define as 0.4-mm pitch BGAs and smaller.

Oftentimes, I'm trying to help customers design products that can also easily be transferred over to Asia and run on mass volume production lines without any advanced requirements that add cost. I work to ensure that prototypes fabricated here in North America are already designed with pre-approved stack-ups to run without modification at the final production

## freedom of design

Isola's RF/MW products provide superior solutions to your RF/MW challenges.

502

## RFASS MICROVALE HIGHLY ENGINEERED MATERIALS

© 2019 ISOLA GROUP. ALL RIGHTS RESERVED.

## Astra<sup>®</sup> MT77

Astra® MT77is an ultra low-loss dielectric constant for 77 GHz automotive radar and sensor designs, long antennas, DAS & CPE antennas, feed networks and millimeter wave frequency applications and is a cost-effective alternative to PTFE.

## I-Tera® MT40

I-Tera® MT40 is a very low Dk Df resin system up to 20 GHz. Used in daughter card, back-plane and hybrid designs, it's a highly reliable system for sequential lamination, lead-free assembly, blind and buried via and CAF sensitive designs.

## **TerraGreen**<sup>®</sup>

TerraGreen® is a halogen-free Low Dk Df resin system engineered for such high performance applications as power amplifier boards for 4G LTE base stations, Internet infrastructure and cloud computing.

## IS680 / IS680 AG

IS680 laminate materials exhibit exceptional electrical properties which are very stable over a broad frequency and temperature range. Suitable for many of today's commercial RF/ microwave printed circuit designs. IS680 AG offers an ultra-low Df, making it an extremely cost-effective alternative to PTFE.

#### **RF/MICROWAVE • AEROSPACE & DEFENSE • AUTOMOTIVE & TRANSPORTATION**

FOR MORE INFORMATION

Isola Group 3100 West Ray Road Suite 301 Chandler, AZ 85226 Phone: 480-893-6527 info@isola-group.com

#### **Julie Ellis**

volume site or sites. TTM calls this Seamless Global Transfer, and it works best when implemented in the planning stages of a new design.

I also review designs for cost savings. For example, in Asia, materials are 40 to 50% of a fabricator's cost, compared to less than 20% in the United States. When we get into high-volume manufacturing, optimizing material utilization can save a customer several percent on the final assembly if we can keep a lowered cost on the PCB by planning the PCB dimensions to fit very well on a fabrication panel. If the circuit board is small, TTM often works with our customers to calculate the best multiple-up array with rails for assembly that can still fit optimally on the fabrication panel. The most common fab panel size is 18" x 24", but we also mass-produce 21" x 24" panels at many sites.

**Shaughnessy:** Sometimes, I get the feeling that the designers don't realize how much control they have over the final product. What are some of the common errors that you see coming in that you wish that you could just tell the designer, "If you just did this...?"

**Ellis:** If you just...came to me for your stackup and design rules first, I wouldn't have to tell you that nobody can fabricate this design in mass production. I request of my customers that they come to me at initial startup of a product before they even bother to route any circuitry, because designs get so complicated that it's very challenging for them to go back and make changes if they've violated standard fabrication design guidelines. It's really stressful to explain to an engineer why his design isn't suitable for mass production, so I prefer to avoid that like the plague.

The information I request from the designer includes:

- Initial prototype and final volume production region/sites

- Material type

- Overall thickness

- Layer count

- Layer copper thicknesses

- Layer designations (signal, plane, mixed)

- Smallest component, connector, or BGA pitch

- Smallest expected lines/spaces for plated and non-plated layers

- Drill structures and traces required for fan-out

- Controlled impedance requirements

- Special requirements (require non-standard materials, additional processes, or tighter tolerances)

- High speed, low Df materials

- Plugged or filled vias-in-pad (VIPPO)

- Back-drills

- High voltage or current

- Optical routing

- Dual finish plating

- Edge plating

- Castellations

- Cavities

- Thermal management

- Press-fit holes

I always ask what the minimum BGA pitch is if there's a BGA, because the most difficult component establishes the level of technical capability required. And I can provide basic design guidelines per device pitch. With a 0.4mm pitch BGA, if a customer is trying to run one trace between the pads on internal layers, those traces and spaces can only be 2.36 mil because of the small distance between the pads. Most fabricators don't have the etching capability to do that, and we have to be careful to follow the design guidelines of the fabricators that can support the small lines.

**Shaughnessy:** What sort of mistakes do you see when the design moves to volume production overseas?

**Ellis:** Here's a recent list of common design errors for jobs going into mass production:

- Multiple semiconductor reference designs using a 6-mil drill and 10-mil or 11-mil pad as a through-hole to route a 0.5-mm pitch BGA. A multi-row 0.5mm pitch BGA requires layers of microvias, because we only use mechanical drills, not lasers, for through-holes, and mechanical drills have larger tolerances than laser drills. So with a minimum standard pad of 16mil (= 8-mil drill + 8-mil to maintain Class 2 annular ring), mechanical drill pads are too large for fine-pitch BGA routing. And laser pads, at laser drill diameter plus min 6-mil = 10-mil min, are way too small for mechanical drills.

- Designs that are prototyped in North America with 6-mil drills transferring to China, where the vast majority of fabricators can handle a minimum 8-mil drill size. Check your fabricator's min drill size before routing.

- A circuit board was designed, fabbed, and assembled before anyone realized there were no access pads for functional or in-circuit test anywhere.

- A 6-layer stack-up with 6-mil drills on 10-mil pads going from L1 to L4 and L6 – L3 with dielectrics that are too thick to use stacked microvias and maintain a max aspect ratio of 0.75:1.

- Another semiconductor reference design had 3mil lines and spaces on an outer through-hole layer with VIPPO—viain-pad (filled) and plated over—which requires and extra plating process, which increases the copper thickness before etch.

**Shaughnessy:** In the designers' defense, they would probably say, "We don't know where it's going to be built or whether it's going to be built in Asia." Is it up to them to try and find out where it's going to be built, if it's going to volume, and then get in touch with those manufacturers?

**Ellis:** Absolutely. In the last year, I've had to convert several designs that could have been simple through-hole designs, but they worked with North American suppliers who must have said, "Yes, we can drill a 5-mil mechanical drill with a 10-mil pad on a 0.62" board." That is greater than 10:1 aspect ratio; it's using a 5-mil bit that's not even common for prototype in America, much less in mass production over in China. The poor customers think that they can use very small pads with small drills on through-holes and transfer it to China, but nobody in China can do it.

The poor customers think that they can use very small pads with small drills on through-holes and transfer it to China, but nobody in China can do it.

I may seem overly regimented, but I tell my customers that I'm an equal opportunity—and conservative—designer. With the rules I give them for standard design guidelines, if they're using a halfway decent supplier, they will be able to fabricate their design at many locations, including our competitors. Sometimes, you give away information that's going to help somebody else. But if you don't train your designers correctly in the first place, you're going to be battling designs that you cornered into one factory, and then it's going to be hard for everybody to maneuver, move forward, and grow into higher volumes. I recommend fair design rules for standard production, design permitting, hoping that we end up booking the business. And when the standard rules are too tight to meet requirements, then we may loosen the rules to more advanced capabilities, which increase cost.

**Shaughnessy:** What are some of the guidelines that you give these designers?

**Ellis:** We provide design presentations for different requirements, including BGA and DFM design guidelines and technology capabilities for each TTM fab site. After I've reviewed all the design inputs for specific projects, the siteapproved information I provided the customer includes:

- Stack-up graphic showing Cu layers, dielectrics, and drill structures

- Controlled impedance table, if required

- Mechanical and laser via hole min drill/pad diameters

- Min. lines/spaces for plated/unplated layers based on starting Cu foil thickness

- Design rules for special requirements, as necessary

**Nolan Johnson:** You're saying that you start with a qualification process to figure out what that design team's intent is with the board. How often do you find that they don't know, or are they mostly clear on that by the time they come to you?

**Ellis:** Approximately 80% of my work is with ongoing customers that I have a good relationship with, so I'm their first call for the stack-up, DFM guidelines, and sometimes to help with best PCB or array dimensions for panel optimization. Other customers mostly know where their business is going.

We support a lot of new development customers, so if one happens to be in the electric vehicle or medical space, it's a fair assumption that their PCB assemblies will eventually be manufactured somewhere in a high-volume region offshore. When I confirm Asia production intent on a new stack-up, I verify it with TTM China before sending it for customer review. Sometimes, though, engineers need to test their electronic design. They're in a hurry, and they're very limited for space, so they'll use the prototype guidelines to quickly check functionality. And other designs are limited quantity test boards that will never go into full production.

**Johnson:** For the 20% of your customers that are new to you, do they tend to be as well prepared?

**Ellis:** Not necessarily, although a lot of new "customers" are actually familiar friends who moved from a previous customer. Most designers I work with already have some experience working with a fabricator, and the ones who haven't are normally glad to have the opportunity to learn.

**Dan Feinberg:** The customer can come to you for the entire package and get assistance, ideas, or recommendations regarding help with the initial part of the design.

**Ellis:** Yes. TTM has a design center in Stafford, Connecticut, where we can provide new electronic designs, redesigns, PCB layout, and electro-mechanical designs. Our Anaren division designs and manufactures high-frequency RF and microwave microelectronics, components, and assemblies for the space, defense, and telecom sectors. Our EMS sites in China do full turn-key PCB assemblies and box-builds. We also work with a lot of good design bureaus and can provide referrals to reputable outside resources for work we don't do.

**Feinberg:** Regarding designers working with others in expanding collaboration, what's happening with the designers working with the suppliers? I know that it didn't used to be the case, but it has become more of the case over the last number of years. For example, if a dry-film supplier comes up with a way to do lines and spaces with straight sidewalls with 0.5-mm lines and spaces, would you then go to a photoresist supplier in today's and work with them to discern if they can develop the material that would be congruent with your design?

## Integrated Tools to Process PCB Designs into Physical PCBs

Minimize costs in both PCB fabrication and assembly through maxiumum panel usage.

Quickly and easily specify the PCBs form, fit and function.

Use manufacturing data to generate a 3D facsimile of the finished product.

Ensure that manufacturing data is accurate for PCB construciton.

Verify

Verify and Optimize PCB Designs for Successful Manufacturing

Create Comprehensive Documentation to Drive Fabrication, Assembly & Inspection

800-535-3226 | downstreamtech.com ©2019 DownStream Technologies, Inc. All rights reserved. **Ellis:** No, probably not. TTM has over 30,000 employees with over 2,000 engineers, so there are other people responsible for looking at new technologies and implementing them globally. That's out of my wheelhouse, and I wouldn't have time to pursue it.

**Happy Holden:** Do OEMs come to you, saying, "We need this technology developed," or do you routinely have a roadmap that goes out a couple of years that you show good customers?

**Ellis:** I think both, because they're intertwined. Customers continually push TTM for new product development, which causes us to always increase our technology at our sites. Customers come to us with new technologies that they're looking for, and often, they're driven by the automotive sector, which is running the full gamut from HDI autopilot controllers to thick copper high-voltage applications. TTM executives plan future roadmaps to justify capital equipment expenditures needed to achieve those capabilities. We'll go out of business if we don't keep up with technology, and our technology is improving so rapidly that I can barely keep up with the changes by site.

We'll go out of business if we don't keep up with technology, and our technology is improving so rapidly that I can barely keep up with the changes by site.

**Barry Matties:** That's not terribly surprising because cars are increasingly becoming computers with wheels.

**Ellis:** Right, our cars are becoming entertainment and communication command centers.

**Matties:** You're in a unique position because you work with so many different designers. Is

there a difference in approach between the old guard and the new?

**Ellis:** It depends on personality. Some people naturally have curmudgeon personalities and want to do it their way or the highway, but usually, engineers are big learners. From my perspective, 95% of the people that I work with are amenable to looking at the best ways to optimize their circuits. For the most part, young engineers are glad to receive any advice that we give them for a roadmap to a good project.

**Matties:** Are their skillsets different than those of a 40-year veteran? I hear what you're saying that they're seeking knowledge, but I'm just curious if their approach or ideas are different.

**Ellis:** That's a really good question, and, again, it depends on personality and also company culture. Generally, younger designers are so excited about new designs and problem-solving, so they're fun to work with. Experienced veterans, on the other hand, can be vast sources of knowledge who expand my horizons through our discussions and design analyses. But I've also encountered companies that don't want their engineers to waste their time talking to suppliers, and that culture breeds Wizard of Oz designers who create impossible designs behind their curtains.

**Matties:** You said that about 80% of your customers are repeat customers, so it seems to me that they could streamline the process because they have these parameters from their historical dealings with you, or is that not the case?

**Ellis:** Yes, it is the case. For a customer's stackups and design guidelines, circuit modules are often copied from one design to the next. When other requirements on the new part don't change too much, we can modify an existing stack-up slightly and keep the original design guidelines for the new part. Maintaining history on designs is extremely time-efficient, and I love it when customers give me an old part number for reference on a new similar design so I don't have to reinvent the wheel on

the stack-up and design rules. We can also review the technical queries that came up during CAM on the old part and get them corrected on the new part, so we reduce the Q&A time delay on the new fab.

Very few of our customers can pay attention to the design rules enough to do their own panelization. I have a couple who do, but it would be great if customers were more aware of that. I think everybody gets confused because different sites and regions have varying requirements for the keep-outs required around the fabrication panels for tooling holes, and nobody is sure what width rails an assembler needs on the array to run through production. It's easiest if the PCB designer, fabricator, and assembler work together to get the rules for assembly, and then let the fabricator optimize the array on their production panel.

**Matties:** Right, because this thought up front can help drive cost out in the tail end.

**Ellis:** It does. Recently, I worked on cost-reduction of a North America production part moving to China. By reducing the rail widths on all four sides of the customer-designed array, I was able to increase panel utilization and reduce the unit cost 7.9%.

**Matties:** And when you're talking about 500,000 parts, that can add up quickly. You said that early collaboration is commonly offered as advice. What other advice would you give a designer who is seeking the most successful design and manufacturing experience?

**Ellis:** Talk to your fabricator and assembler and follow the KISS (Keep It Super Simple) principle. From the user's point of view, if something goes wrong and they have to troubleshoot or fix something, a complicated, difficult-to-build design will also be difficult to take apart, repair or rework. Think of your whole system from the outside in, and then start building from the inside out, thinking of the bigger pieces that follow.

**Matties:** I appreciate your time, Julie. Thank you.

**Ellis:** Thank you. Everyone had interesting questions.

**Shaughnessy:** That was fantastic. Thanks a lot.

DESIGN007

#### Feature Interview by Andy Shaughnessy I-CONNECTO07

During SMTA Atlanta, I spoke with Albert Gaines of HiGain Design. We discussed Albert's belief that everything starts with design and that too many engineers and designers focus solely on the final board at the expense of the documentation, which is a designer's most important product. Do you consider your documentation to be a critical product?

**Andy Shaughnessy:** Albert, you are the founder, chief cook, and bottle-washer for HiGain Design. A minute ago, we were talking about how everything in electronics manufacturing really starts with design. You had an interesting point about some things that designers and design engineers sometimes neglect to consider early in the cycle.

**Albert Gaines:** I've been doing board layout since '81, and I came through the drafting side of it. Documentation was our product. I think most engineers today lose the concept of the fact that the final product is not the prototype. They finally have it working, but they think they're through. But their product is documentation—the Gerber package, ODB++ package,

## Albert Gaines: Design All Comes Down to Documentation

testability, assembly drawings, and all of the firmware. That documentation and traceability of that documentation is their product—not what's sitting in the test lab.

**Shaughnessy:** How did we get to this point? I'm sure that there are people who have been doing this for 30 years and have never looked at the documentation as their final product.

**Gaines:** A lot has changed over the years because we've had a shift to where more EEs are doing more board layout, and we don't have documentation departments in companies. Everybody is running freelance in their own cubicles. Nobody is enforcing what the documentation has to be. Ultimately, you end up with a board shop or an assembly house with a big void, wondering, "Am I going to get this data, the IPC-356 netlist, or the bare testing of the board? Or am I going to get an ODB++ for pickand-place? What am I going to get? Do we have to recreate it after the fact?"

**Shaughnessy:** We always joke about how the designers get blamed for everything, but this sounds like one of the things that designers need to be aware of; it's more about the documentation than anything else.

## DRIVING TECHNOLOGY TO NEW EXCELLENCE

Multilayer, HDI, Bendable, Flex/ Rigid Flex, High Frequency PCBs and more

#### ABOUT CML

CML are the leaders in printed circuit board (PCB) sourcing solutions. CML's mission "We care about reliable connections," apart from the reliable connections of our PCBs, paramount importance is also placed on the relationship between CML, our customers and suppliers.

CML provides a wide product portfolio and an umbrella of services ranging from consultancy, design, engineering, manufacturing and logistics for all markets - convenient and reliable.

CML has a global network, located across 17 international cities and a local presence with a multilingual and culturally diverse team.

### Contact our USA office today

+1 650 269 4823

### For information on our other offices, please visit our website:

http://www.cml-globalsolutions.com

CB WEST 2019 Santa Clara, California

**Gaines:** Yes. It would be very good for each designer to have a checklist beside their desk when they're getting ready to finish a product, detailing what they need to do-not just generate Gerbers and NC drill files and send it over the fence to a board shop. When I output documentation, I have folders for assembly data, bare board data, and testing data, and everything goes in each particular folder. If something's for assembly, you grab the whole folder, which has anything that may deal with the assembly world or test world or bare board. It's good to have that reminder. Another resource is your magazines. You've published information on what average documentation looks like, but I wonder how many designers look at that list and say, "What is that?" They don't even know what it is.

**Shaughnessy:** I know that the post-processing part is usually a designer's least favorite part of the cycle. Designers focus on the board and not documentation.

**Gaines:** Right. I love engineers, and I've worked with a lot of great ones, but many of them tend to be detail-oriented regarding the circuit de-

sign. But from a board layout standpoint and what is required from that point on, they were probably never taught it. They're just flying by the seat of their britches, and when somebody tells them to get it, they'll do it. I went to the Design-2-Part show a while ago in Atlanta, and I met with a company who told the guy who had done their board layout that they needed a basic netlist out of the software, but he didn't even know what he was talking about. Many don't know what they don't know.

**Shaughnessy:** Right, and how do we show them? What can we do about it?

**Gaines:** I love webinars; they're one of the best, cheapest formats for information out there. If I'm doing a board layout, I'll pop a webinar up on the screen, even if it's something I'm not interested in, just to broaden my knowledge. If I get five minutes' worth of information out of that one-hour event, that was time well spent.

**Shaughnessy:** Engineers and some designers still don't realize how much power they have at their station. To some extent, they can control the cost of the final product and the re-

liability, and I still think they sell themselves short in a way.

**Gaines:** Sometimes, designers look at board shop specifications of what they can do, not that the board needs that tight of geometry, but they can do it, so that's what they put on the circuit board. Some eight-layer boards that could easily be reduced to six-layer boards, or 14 reduced to 10. Just look at it, decide what you need, and don't think, "I'm just trying to do a board and get it off my desk."

**Shaughnessy:** Because everybody's rushed.

**Gaines:** In this world, if you're not rushed, then you're probably not needed (laughs).

**Shaughnessy:** What advice would you give to a new designer on how to take control and be aware that they can help make the product profitable?

**Gaines:** Look at a broad spectrum of standards of what's required for different designs. Technologies will drive what you're going to have to do with space and clearance, but don't put yourself in a corner. Be open to other people's opinions because one supplier on this product may ask for something while another supplier may ask for something completely different. You need to be understanding and ask questions. Make a list of what you need for the next time you're going back through it again.

I have default output files that I call up with everything; all I have to do is change a file name, click a button, and it outputs everything. I don't care if it's a board with four parts on it or one that has thousands. They all output the same pack of data. I send everybody that data, and if they choose not to use half of it, that's fine. I won't get a call back, saying, "Please send me this." Too much data is probably the right amount.

Shaughnessy: That's good. Thanks, Albert.

Gaines: Thank you, Andy. Good to see you. DESIGN007

## KLM Partners With TU Delft to Make Aviation More Sustainable

KLM President and CEO Pieter Elbers and Dean of the Faculty of Aerospace Engineering at Delft University of Technology (TU Delft) Professor Henri Werij have signed a new cooperative agreement to work together on making aviation more sustainable at the IATA Annual General Meeting in Seoul.

KLM will be contributing towards TU Delft's research into an innovative flight concept known as the "Flying-V," which embraces an entirely different approach to aircraft design, in anticipation and support of sustainable long-distance flight in the future.

Although the plane is not as long as the A350, it does have the same wingspan. This will enable the Flying-V to use existing infrastructure at airports, such as gates and runways, without difficulty and the aircraft will also fit into the same hangar as the A350. What's more, the Flying-V will carry the same number of passengers–314 in the standard configuration–and the same volume of cargo, 160m<sup>3</sup>.

The aircraft's v-shaped design will integrate the passenger cabin, the cargo hold and the fuel tanks in the wings. Its improved aerodynamic shape and reduced weight will mean it uses 20% less fuel than the Airbus A350, today's most advanced aircraft.

The Flying-V is propelled by the most fuel-efficient turbofan engines that currently exist. In its present design, it still flies on kerosene, but it can easily be adapted to make use of innovations in the propulsion system-by using electrically-boosted turbofans, for example. (Source: KLM)

## **Design for the Unknown**

#### Feature by Kelly Dack, CID+

Our industry loves DFX, also known as the "Design Fors." As PCB designers, we not only design for manufacturability (DFM) but we design for assembly, reliability, cost, test, and many more factors which we like to lump together as DFX. But now, I think it's time we embrace a new DFX: Design for the Unknown, or DFU.

I'm a firm believer that electronics development really does start with the PCB designer. I am a big fan of Stephen Covey's *The 7 Habits of Highly Effective People.* I especially like to practice habit No. 2 when beginning a new PCB project: Start with the end in mind. All too often, project teams seem to push ahead with only what is known about a project at the time, even to the point of starting the PCB layout. Proceeding on risk is a strategy that project teams use to make progress on a project despite not having all of the data or constraints. But proceeding on risk may have only a small chance of working out. When incorrect assumptions are made about a product, great amounts of resources will most certainly be wasted. Years ago as a salaried PCB designer, I'd eagerly pushed ahead on design layouts overnight, on risk, only to be informed by a program manager the next morning that an assumed board outline or component needed to change. This affected the entire layout! Assumed risk in these cases obliterated hundreds of healthy sleeping hours of my life that I'll never get back. I needed a new strategy.

Thereafter, besides committing to design PCBs on an hourly basis, I sought to discipline myself to get all of the blanks filled before starting a PCB layout. I would do better at starting a PCB layout with the end in mind because "the end" is the culmination and validation of so many critical details which the design started with in the first place.

### STRIVE FOR **EXCELLENCE** www.emctw.com | EMC.INFS@mail.emctw.com

EM-890/ EM-890K Green Laminates are ready to transcend your future 200G and 400G applications

### INDUSTRY'S FIRST HALOGEN FREE ULTRA LOW LOSS MATERIAL

World's largest producer of environmental friendly advanced laminate materials

The Best-in-class SI Performance At least 5~10% lower insertion loss than competition

Ideal for multiple lamination cycles (>5x)

Compatible with FR-4 Hybrid Design for economical Hybrid solutions with EM-827 or EM-370(Z)

Excellent Thermal Properties for Ultra Fine BGA Pitch (Pass 10X LF260 IR Reflow and IST > 1K cycles with min. BGA pitch <0.7mm)

Outstanding Anti-CAF performance (Pass 85°C/ 85% RH/ 50~100V/ 1K hours with 0.8mm BGA pitch )

North American Master Distributor 1-800-909-8697 • www.technica.com

Where will this PCBA be manufactured? What types of equipment will be used? What are the potential volumes? What is the environment in which the PCBA will operate? How about that materials list—are we sure all of the parts are available? It all begins with design and to me, designing with the end in mind means putting all of the parts together in an organized way which would facilitate meeting all of the PCB performance and manufacturing constraints.

But in the past, I found myself waiting for the blanks to be filled in. The project timelines began to slip and I had not even begun placement of any of the parts. Slap! (Figuratively, of course.) I vowed to never again find myself in the awkward position of having nothing to show at the end of a project timeline. "I'm waiting on…" is never a good strategy. Corporate management folks who report to stockholders would rather show a poorly designed PCB progress as opposed to no PCB at all.

"The end" is filled with a myriad of details which must be considered in order to do a good job of putting the *Design* in our DFX acronym. Sometimes the design constraints at the start of a project appear fuzzy or nonexistent. Sometimes, even during the project, the goal posts change width or distance. There is rarely a perfect scenario in the world of project timelines, communication and time-to-market constraints.

One obvious question: "How can you design for something you can't see?" You can't, but you must. At the start of a project, unknowns will exist. You must develop the attributes of a detective to anticipate potential fallout from the unforeseen and use practical techniques to design around them.

Times have changed. We used to hear a great deal about the benefits of products that were "designed from the inside out." Back when automobiles were the size of large boats, we often saw ads featuring a human silhouette poised in a comfortably seated position. Roominess and comfort seemed to be the selling point of these ads. Bigger was better back then.

#### The Rise of the Industrial Designer

Today, smaller is better, and industrial designers typically have the first say on the overall size, shape, texture and color of a product. Products are rarely designed from the inside out now. Over time, advancements in materials and technology have offered enhanced capabilities within increasingly smaller and smaller packages.

Now, I have spent a great amount of time writing and speaking about how important it is for PCB designers to consider all of the downstream stakeholders of a PCBA project. I like to think of design as the hub of a product's success; we must consider the needs of all of our manufacturing stakeholders downstream. If the PCB incorporates all of the DFs—design for manufacturability, design for cost, design for test, etc.—then the product is sure to be a success, right?

Well, the industrial designers of today may be akin to the fly in the designers' proverbial oatmeal. These folks are *creatifs* whose design methodology cannot always follow the considerations of DFX. They often work directly for the inventor. Their job is to conceptualize and please the inventors, their marketers and their investors. When marketing wants the product smaller, the industrial designer can whip out a pastel marker or tap out a keystroke using some artistic software and shrink the hell out of the package envelope to the applause of the inventor while in total disregard for the unforeseen challenges they may be creating for their downstream PCB stakeholders.

"Shrinkage" was an unfortunate, unforeseen problem featured in the 85<sup>th</sup> television episode

of "Seinfeld" in 1994. But since 1994, the unforeseen challenges presented by industrial designer's shrinking packages and its effect on IPC levels of manufacturing producibility has only made PCB design packaging and layout more perplexing. With package shrinkage, the typical product design iteration cycle goes something like this:

- 1. Product invention requires competitive advantage in capability, size and cost shrinkage

- 2. Product idea goes to industrial design to be aesthetically and ergonomically conceived

- 3. Product renderings go to mechanical engineers to create enclosure tooling

- 4. Product specifications go to Electronics engineers to locate electronic parts

- 5. Electronic parts are placed into schematic and BOM

- 6. PCB designer begins layout with PCB outline and keep-outs from ME and BOM and schematic from EE

- 7. Only 50% of parts will fit on PCB outline.

- 8. EE must shrink parts and consider two-sided assembly

- 9. PCB designer manages to fit parts within PCB outline though part-to-board outline spacing is compromised. Some clearance issues are mitigated by shrinking some land pattern geometry though solder joint reliability is now compromised

- 10. Another problem arises: limited board surface real estate on board surfaces for routing

- 11. PCB design must go to multilayer stackup to allow routing and power distribution

Now, the PCB cost quotation exceeds the target cost model for the project. It is only at this point, far downstream from the concept renderings phase, that the entire product must be re-evaluated for feasibility.

Rinse and repeat the entire process. Or we can try to change this process. After all, we'll never get back this wasted time and resources.

### **Design For the Unknown**

As PCB designers in this early, critical stage of design, we served as the project team's reality checker. We didn't really get to design much at all. Too many critical PCBA design attributes and constraints were unforeseen by the upstream stakeholders, rendering the concept unfeasible in this configuration. So now that the project is a prime candidate for DFU (or a redesign), how can a design team do a better job?

Project teams must embrace the concept of designing with the end in mind. From project conception on, everything will flow downstream. After all, what river raft guide would float a team of tourists down an unknown, unnavigated river?

While the design is still in the earliest stages, check in with all of the knowledgeable folks downstream—the PCB designers and all of the process stakeholders who reside downstream and gain their design feedback. When you're in DFU mode, you will avoid the perils of the unforeseen. Design and, if necessary, redesign with the end in mind and try leaving a little bit of extra space to make any future DFU efforts more navigable.

I hope that by working with Design007 on this idea, we can start an industry-wide discussion about DFU, and how this can help all of the stakeholders involved in developing electronic products. Feel free to drop me a line, and let's get this conversation going! **DESIGN007**

**Kelly Dack** is an IPC CID instructor with EPTAC. He has over 30 years of experience in PCB design. To contact him, click here.

## Clear Communication Takes the Cake

#### Tim's Takeaways Feature Column by Tim Haag, CONSULTANT

An amazing thing happened just a few days ago, but before I go into detail about it, let me give you a little context to better explain it. First, let me be blunt; I am not a chef. Yes, I did spend time flipping burgers professionally as a teenager, but other than that, my repertoire of culinary delights is pretty limited. A lot of this has to do with my lack of patience. Let's face it; when it is time to eat, I hate trying to figure out how to cook it.

Coincidently, this lack of patience has made me very popular with the fast food industry. Aside from some breakfast items (including a really cool breakfast sandwich), minute rice, and exploding chicken on the barbecue, I'm kind of a dunce in the kitchen. If it's peanut butter and jelly sandwiches or microwaving leftovers, I'm your guy. But for everything else, I am way out of my league.

That is why I have to honestly wonder what in the world I was thinking a couple of days ago when I decided to make a cake for my wife on her birthday. I had already ordered a storebought cake for the occasion (it was a chocolate-chocolate chip Bundt cake if you wanted to know), but then she mentioned that poppy seed was her most favorite cake flavor ever.

You can never have too much cake for your birthday, I reasoned, so I declared that this was going to be the year of the over-abundant birthday desserts. After a little research, though, I found out that there wasn't a bakery close enough that could provide me with a poppy seed cake, so I decided to make it myself. "What could go wrong?" I thought, forgetting for the moment about the exploding chicken on the barbeque incident, which caused the backyard neighbors to nearly call the fire department. It should also be noted that I had never baked a cake before—not even from a box mix. Realistically, my chances of success were not good.

Figure 1: Perfectly baked poppy seed birthday cake.

The amazing thing that I first mentioned that was a real shocker was that the cake turned out perfectly (Figure 1). It raised like it was supposed to and tasted delicious. My wife absolutely loved it, and all of the neighbors celebrating with us were equally impressed. As much as I would love to pat myself on the back and take a bow on center stage, the truth is I owe this success to one thing and one thing only: I had

## Offshore pricing. Exceptional quality. Local service.

We strive for excellence in everything we say and do.

Our finger is on the pulse of the latest technologies, systems and solutions in an effort to be a total PCB solution provider for our customers.

### Why choose Eagle as your total PCB provider:

- . Dedicated offshore team with local quality and engineering support

- Seamless transition from prototype to production

- . The same exceptional service and support that you've come to expect from Eagle

Click here to learn more about our offshore option

a great set of instructions and an easy-to-follow recipe for making this cake.

No matter if you are baking a cake or building a circuit board, it's all about clear communication. If the person writing the recipe had not made the choice to clearly communicate what their intentions were for baking that cake, I would have been lost. A missing ingredient here or an incorrect oven temperature there and my birthday surprise would have ended up in the garbage in the same way a successfully built circuit board starts with clear communication from the designer. Circuit board manufacturers want to create a perfect PCB for you, but they can only do so to the extent of the instructions that you give them. Everything truly does start with design, and whether you have success or not is up to you and how you communicate it.

To clearly communicate your "recipe" to your board manufacturers, you need to make sure that you include all of the data that they will need to get the job done correctly. This will include variations of the following data files at a minimum for both fabrication and assembly:

- **PCB image files:** These are typically Gerber formatted data files with their accompanying apertures assignments

- **NC drill files:** Excellon formatted data files that have been the standard for years

- Fabrication drawings: These should include board layer stackup information and drill sizes with their quantities and locations; they should also include dimensions of the board and any unique cutout features as well as detailed notes for the fabrication of the bare PCB

- Assembly drawings: These should include component locations and their reference designators as well as unique assembly details, such as mechanical f eatures and any necessary mounting hardware; there should also be callouts for markings and labels as well as detailed assembly notes

- **Bill of materials (BOM) report:** This will be a data file that lists the details of each part on the circuit board

- **XY location file (pick and place):** This report details the XY location of each part on the circuit board for automated assembly equipment

- Netlist: This file will include all of the connectivity of the PCB for automated test routines that will be run by the manufacturer

As I said, this is just the minimal amount of data to tell your manufacturer what your PCB design needs to be built. You can do a lot more to improve communication and make your intent even clearer.

When I was baking the cake, I had a great set of instructions in the recipe I used. But the problem was that I didn't necessarily understand all of the detailed instructions in the recipe. For instance, I didn't understand what it meant to "butter and flour the cake pan," or "fold the eggs into the mixture." Hey, don't laugh; if you've never done this before, you might wonder how you "fold" eggs as well. Fortunately, I was able to find some help from online videos, and I quickly learned these little treasures of successful baking techniques.

In the same way, we too can add additional helpful instructions to our manufacturing files in the form of "README" files. These can be as simple or as complex as you want to communicate information that is above and bevond what you already have in your regular manufacturing files. The key is to make everything as clear as possible with your manufacturer. This also includes providing them with your design database if necessary. Many PCB contract manufacturers now prefer working with your entire PCB design database, especially when building prototype boards. This way, they have immediate access to schematic and netlist information that they know is synchronized with the layout information.

Another way to give your manufacturer more complete information is to use an IPC-2581 formatted output file. These files contain all of the PCB manufacturing data that the fabrication and assembly shops need to build your board. Many PCB design systems now have the capability to export manufacturing data in this for-

## UPGRADE YOUR KNOWLEDGE

Learn about **COMMON DFM ISSUES** in our latest e-book and view our growing library of resources created by the PCB design experts at EMA Design Automation.

mat with a push of a button. You should give this format some serious consideration if that is an option for you and your manufacturer.

Now, if you will forgive me for droning on and on about this cake that I created, there is one more comparison in this story that I would like to explore. I would not even have known that poppy seed was one of my wife's favorite cake flavors if I had not been talking to her about it first. I also wouldn't have known about some of the baking tips that I needed if I had not talked to my daughter-in-law and others about how best to do this. My point is that the most effective communication starts before you are ready to build the product so that you are ready for the task ahead.

One of the best things that you can do for yourself when getting your PCB design built by a manufacturer, is to begin talking to them before you start the design. I have heard fabrication and assembly people talk about the successes they've had working with the designer ahead of the build, and the problems they've experienced when there hasn't been adequate communication. The more communication they have with you, the better the results are likely to be.

Here's a little design treasure that I learned a while back, and hopefully it will be helpful to you too. Your manufacturers know a lot about building circuit boards because it's their job to know, and they wouldn't still be in business if they didn't have this knowledge. They have a very good understanding of PCB materials and layer stackups and what needs to happen to configure the board for the type of design that you are doing. Ask them for help if you don't understand, and listen to their different options for performance, price, and manufacturability. With their expertise, they will be able to narrow the options down for you to give you the best value and performance for the money that you will be spending.

Remember that clear communication is the key to getting the job done right. Just as a wellwritten recipe helped me to be the big hero a couple of days ago on my wife's birthday, open communication and clear instructions help you to be the hero on your next PCB design. Everything starts with design, and that means that you have to take charge of making sure that everybody knows what you need to be done for the job to be successful. Now, if you will excuse me, there's only one slice of that cake left, and I want to snag it before someone else beats me to it. **DESIGN007**

**Tim Haag** is a PCB design consultant based in Portland, Oregon. To read past columns or contact Haag, click here.

## **New Interaction Between Thin Film Magnets Discovered**

We ubiquitously stream videos, we download audiobooks to mobile devices, and we store huge numbers of photos on our devices. In short, the storage capacity we need is growing rapidly. Researchers are working to develop new data storage options. One possibility is the racetrack memory device where the data is stored in nanowires in the form of oppositely magnetized areas, so-called domains.

A research team from Johannes Gutenberg University Mainz (JGU) in Germany, together with colleagues from Eindhoven University of Technology in the Netherlands as well as Daegu Gyeongbuk Institute of Science and Technology and Sogang University in South Korea, has made a discovery that could significantly improve these racetrack memory devices. Instead of using individual domains, in the future one could store the information in 3D spin structures, making the memories faster and more robust and providing a larger data capacity.

The Mainz-based researchers examined a number of different combinations of materials grown in multilayers. They were able to show that this previously unknown interaction exists in different systems and can be engineered by the design of the layers. This opens up the possibility of designing various new three-dimensional spin structures, which could lead to new magnetic storage units in the long term.

(Source: Johannes Gutenberg University Mainz)

### The electronics

found in every system keep us going with the **ones** we'd go the **distance** for

START WITH THE Guality. STANDARDS Quality. Reliability. Consistency. IPC.

#### **IPC Serves the Electronics Manufacturers That Serve Humanity**

Billions around the globe rely on electronics to improve their quality of life. Thousands along the entire electronics industry supply chain rely on an IPC membership to consistently manufacture highly reliable, high-quality products in the sectors where excellence is of the utmost priority, including:

Automotive/Transportation | Medical Devices | Aerospace Defense Industrial Manufacturing Telecommunications

Your products benefit the world. IPC will benefit your bottom line. Join IPC at startwiththestandards.ipc.org.

# WHAT DO YOU THINK?

# Technically Appropriate Material Choices Are Key to Success

#### Feature Interview by Nolan Johnson

Materials are no longer a passive part of the design; they play an active role in the manufacturability, reliability, and speed of a PCB. I-Connect007's Nolan Johnson and Mike Creeden, founder of San Diego PCB Design, discuss several key characteristics that designers should consider in their material selection process.

**Nolan Johnson:** Mike, could you introduce yourself and tell us about what you're working on?

**Mike Creeden:** I'm the founder of San Diego PCB Design, and I had the opportunity to sell the company to Milwaukee Electronics/Screaming Circuits, so we've joined the Milwaukee Electronics family of companies. I also serve as an EPTAC instructor for the IPC CID and CID + programs as an MIT (master instructor).

**Johnson:** We're focusing on the latest developments in materials, and it's important to get a designer's perspective. Who do you

see as being the leading companies in this segment?

**Creeden:** When I think of the different materials and products that are out there, one company comes to mind. So, I'm going to give some props to Insulectro, which is a distributor for many of the major laminate material products. I want to talk about them because there's a difference between good and great companies. A great company is one willing to go outside of the norm, do something that helps the designer, and supports technology development.

Their main customers are fabricators, yet time and time again, I've seen them supporting designers by trying to enhance their technical knowledge and capabilities. San Diego PCB has been collaborating with Insulectro for several years now and is looking for ways to collaborate more. They're helping us to design better, and we're utilizing products in a timely manner as they're helping us solve our customers' problems. To me, Insulectro is a significant player in this electronics material industry.

# Candor Circuit Boards

# Innovative solutions for complex circuit board manufacturing

Click to see what we bring to each sector of the industry:

RF/Microwave PCBs

Automotive Electronics

Power Electronics

Lamination

High-Speed Data

Startups

Our technology produces what our customers dream!

#### www.candorind.com | (416) 736-6306

**Johnson:** Could you give some examples regarding how they're helping and contributing?

**Creeden:** Absolutely. When I'm challenged with real estate and cannot put the required capacitors on the board because I have BGAs on both sides of a board, the team at Insulectro is a resource I can go to and ask for technology help. They suggested buried capacitance materials, which helps my power delivery and filters out noise on the

**Mike Creeden**

board. Another example is that we're seeing a lot more rigid and rigid-flex circuits. Insulectro has coached us to utilize materials that are appropriate for these types of boards, which has helped us grow in our understanding of rigid-flex development.

Further, they point us toward their fabrication partners, which is their customer base, and this helps us understand both the material and process. There's always a learning curve for designers when it comes to rigid and rigid-flex. Some of the Pyralux materials that DuPont brings have also been useful for us trying to get our product right from the beginning. Additionally, I'm seeing more microcircuitry and some very fine features that pose a challenge. Some of the dry-film materials that DuPont offers help us with circuits that require accuracy in the definition of microfeatures.

**Johnson:** What's intriguing to me is that you're talking about materials early in the process. You're talking to materials experts as you're trying to figure out the layout of the board. When in the design cycle should PCB development people consider material selection?

**Creeden:** That's a great question. It should be within the first days of starting your project because that's the best time to establish that things will be designed "correct by construction." I do not want to design a product and then consult my fabricator in the last days of development. If the material is not in stock, we

may be delaying the procurement of what is probably a late design, anyway. You'd want to make sure that it's in stock, and you'd also want the coaching from your fabricator and supply chain to make sure that you're making correct selections. When you do this late in the process, selections may happen quickly, and there may not be enough time to ensure that it's an appropriate material selection. There's always a material technology decision,

and it should be made early in the design process. The earlier, the better because this allows time to change it if that is required.

**Johnson:** You're making the point that material is becoming increasingly important. With that in mind, and especially for anybody who's newer to this, why is material important?